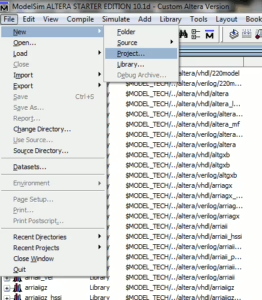

FPGA jsou velmi rychlé a moderní obvody , které nacházejí uplatnění ve velkém množství aplikací díky své flexibilitě, rychlosti a možnostech. FPGA (či CPLD) mají však vlastní programovací jazyk – VHDL (a/nebo Verilog), který se velmi liší od ostatních jazyků (C atp.). V tomto návodu, nebo jestli chcete – ukázkách funkčních programů, se nebudeme zabývat popisem VHDL (jeho základy), ale pouze funkčními programy. V tomto dílu se bude jednat o hradlo AND a napsání tzv. test bench. To je program, kterým testujeme jednotlivé stavy vývodů a zobrazujeme jejich stav. Jako velmi dobrý základ doporučujeme knihu: Číslicové systémy a jazyk VHDL, od autorů: Jiří Pinker a Martin Poupa z roku 2006, nakladatelství BEN

Článek – VHDL – hradlo AND

Autor: Petr Šrámek

Tagy:

Komentáře:

121 komentářů na sociálních sítích

@TomasBajer Já mám páječku z tindie, která používá weller hroty a je skvělá, ale můj styl práce je více opravování než pájení a ta pinzeta se mi hodí více... a dost lituju, že jsem nepřikoupil větší hroty :-D ...více

Číst komentáře

- a -

Přidat svůj názor- a -

Ukaž světu,

že jsi Maker!

Koupit tričkože jsi Maker!

Související články

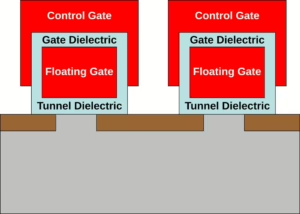

Firma Apacer uvede na trh v průběhu roku 2018 produkty založené na 3D NAND TLC FLASH pamětech.

Žádné sociální komentáře k dispozici.